MARVELL

## 88SB2211

PCI Express-to-PCI Bridge

## Datasheet

Doc. No. MV-S104870-U0, Rev. B February 27, 2008, Preliminary

| Document Conventions |                                                     |                                          |  |

|----------------------|-----------------------------------------------------|------------------------------------------|--|

|                      | Note: Provides related information or               | information of special importance.       |  |

| ļ                    | Caution: Indicates potential damage t               | o hardware or software, or loss of data. |  |

| Ļ                    | Warning: Indicates a risk of personal injury.       |                                          |  |

| Document Status      |                                                     |                                          |  |

| Doc Status:          | Doc Status: Preliminary Technical Publication: 0.xx |                                          |  |

For more information, visit our website at: <u>www.marvell.com</u>

#### Disclaimer

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in these types of equipment or applications.

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees:

<sup>1)</sup> Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control

Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2; 2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are

<sup>2)</sup> Not to export the direct product of such technology of such soliware, to EAR Country Groups D.1 of E.2, it such technology of soliware and direct products thereof are controlled for national security reasons by the EAR; and,

<sup>3)</sup> In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant, not to export to EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons by the EAR, or is subject to controls under the U.S. Munitions List ("USML").

At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any such information.

Copyright © 1999–2008. Marvell International Ltd. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, Fastwriter, Datacom Systems on Silicon, Libertas, Link Street, NetGX, PHYAdvantage, Prestera, Raising The Technology Bar, The Technology Within, Virtual Cable Tester, and Yukon are registered trademarks of Marvell. Ants, AnyVoltage, Discovery, DSP Switcher, Feroceon, GalNet, GalTis, Horizon, Marvell Makes It All Possible, RADLAN, UniMAC, and VCT are trademarks of Marvell. All other trademarks are the property of their respective owners.

## 88SB2211 PCI Express-to-PCI Bridge

Datasheet

### Marvell. Moving Forward Faster

### **Product Overview**

The Marvell<sup>®</sup> 88SB2211 X1 PCI Express to 32-bit PCI bridge connects legacy PCI parallel bus devices to the new, advanced serial PCI Express interface. The 88SB2211 is a PCI Express-to-PCI forward and reverse bridge. It is fully compliant with the PCI-SIG PCI Express-to-PCI Bridge Specification.

### Features

- Marvell 88SB2211 X1 PCI Express to 32-bit PCI Bridge

- PCI Express-to-PCI/PCI-X Bridge Specification 1.0 compliant

- Forward transparent bridge

- Single PCI Express 1.0a X1 port

- Single 32-bit PCI2.3 33 MHz port

- Single TWSI port

- Eight General Purpose I/O pins

- Single 3.3V power supply

- 64-bit addressing support

- VGA and ISA addressing support for legacy operation

- Adjustable read prefetch algorithm

- Access to all internal registers from the PCI Express port (in Forward Bridge mode only)

- IEEE Standard 1149.1 JTAG Interface

### PCI Express Interface

- PCI Express Base Specifications, Revision 1.0a compliant

- Integrated PCI Express PHY based on proven Marvell SERDES technology

- X1 link width, at 2.5 GHz signaling

- 100-MHz differential PCI Express reference clock generation, saving an external oscillator

- Link CRC

- Lane polarity reversal support

- 128-byte Maximum Payload Size (MPS)

- Single Virtual Channel (VC-0)

- Advanced error reporting capability

- · Up to four master non-posted requests outstanding

- · Up to four target non-posted requests outstanding

- Interrupt emulation message support

- Error message support

#### PCI Interface

- PCI Local Bus Specifications, Revision 2.3 compliant

- 32-bit, 33 MHz operation

- 3.3V, 5V tolerant

- · Internal arbiter support for five external masters

- PCI clock source for up to five external agents

- Fast Back-to-Back capable

- Up to four active target delayed reads

### Power Management

- Advanced Configuration Power Interface Specifications (ACPI) compliant

- Supports all device power management states: D0, D1, D2, D3Hot, and D3Cold

- Supports D3Cold wake-up events upstream forwarding (PMEn/WAKEn)

### Two Wire Serial Interface (TWSI) Port

- Optional EEPROM initialization

- Internal register access

- Forward Bridge Applications

- ATCA PCI Express based platforms

- PCI extension for server, desktop, and mobile motherboards

- ExpressCard and MiniCard applications

- Split chassis platforms

- PCI Express docking stations

- Reverse Bridge Applications

- PICMG based platforms

- PCI Express extensions for PCI platforms

- PC-Card (PCMCIA) and Mini-PCI applications

- LQFP128, 14 x 20 mm package, 0.5 mm pitch

## **Table of Contents**

| Prefac | ce                                                  | 8  |  |

|--------|-----------------------------------------------------|----|--|

|        | About This Document                                 | 8  |  |

|        | Related Documents                                   | 8  |  |

|        | Document Conventions                                | 9  |  |

| 1      | Overview                                            | 10 |  |

| 2      | Pin Information                                     | 11 |  |

| 2.1    | Summary List of Functional Pins                     | 12 |  |

| 2.2    | PCI Express Interface Pin Assignments               | 14 |  |

| 2.3    | PCI 32-bit Interface Pin Assignments                | 15 |  |

| 2.4    | Reset Pin Assignments                               | 17 |  |

| 2.5    | TWSI Interface Pin Assignments                      | 17 |  |

| 2.6    | JTAG Interface Pin Assignments                      |    |  |

| 2.7    | GPIO Interface Pin Assignments                      | 19 |  |

| 2.8    | Analog Interface Pin Assignments                    | 19 |  |

| 2.9    | Power/Ground Pin Assignments                        | 20 |  |

| 3      | 88SB2211 Pinout                                     | 21 |  |

| 4      | Reset Configuration                                 | 23 |  |

| 4.1    | Pins Sample Configuration                           | 23 |  |

| 5      | Electrical Specifications (Preliminary)             | 27 |  |

| 5.1    | Absolute Maximum Ratings                            | 27 |  |

| 5.2    | Recommended Operating Conditions                    |    |  |

| 5.3    | Power Dissipation                                   | 29 |  |

| 5.4    | Current Consumption                                 |    |  |

| 5.5    | DC Electrical Specifications                        |    |  |

| 5.6    | AC Electrical Specifications                        |    |  |

| 5.7    | 7 Differential Interface Electrical Characteristics |    |  |

| 6      | Thermal Data                                        | 44 |  |

| 7      | Package Mechanical Information                      | 45 |  |

| 8      | Part Order Numbering/Package Marking                | 47 |  |

|        |                                                     |    |  |

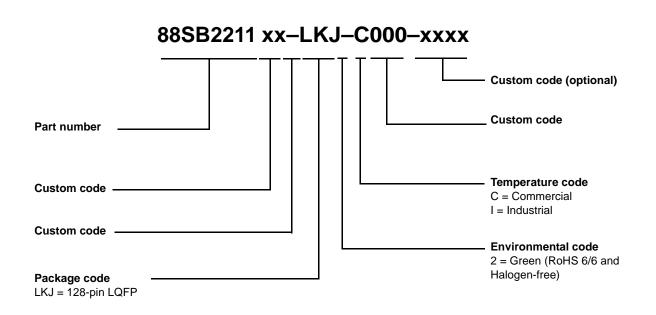

| 8.1    | Part Order Numbering                                | 47 |  |

| Α   | 88SB2211 Register Set |  |

|-----|-----------------------|--|

|     | Registers Overview    |  |

| A.2 | Register Description  |  |

| в   | Revision History      |  |

## **List of Tables**

| Table 1:   | Pin Assignment Table Conventions                                       | 12  |

|------------|------------------------------------------------------------------------|-----|

| Table 2:   | Functional Pin List Summary                                            | 12  |

| Table 3:   | PCI Express Interface Pin Assignments                                  | 14  |

| Table 4:   | PCI 32-bit Bus Interface Pin Assignments                               | 15  |

| Table 5:   | Reset Pin Assignments                                                  | 17  |

| Table 6:   | TWSI Interface Pin Assignments                                         | 17  |

| Table 7:   | JTAG Pin Assignments                                                   | 18  |

| Table 8:   | GPIO Interface Pin Assignments                                         | 19  |

| Table 9:   | Analog Interface Pin Assignments                                       | 19  |

| Table 10:  | Power/Ground Interface Pin Assignments                                 | 20  |

| Table 11:  | 128 LQFP Pinout Pin List by Pin Number                                 | 22  |

| Table 12:  | Reset Configuration                                                    | 23  |

| Table 13:  | Absolute Maximum Ratings                                               | 27  |

| Table 14:  | Recommended Operating Conditions                                       | 28  |

| Table 15:  | Power Dissipation                                                      | 29  |

| Table 16:  | Current Consumption                                                    | 30  |

| Table 19:  | Reference Clock AC Timing Specifications                               | 32  |

| Table 21:  | PCI Interface Measurement Condition Parameters                         | 35  |

| Table 25:  | PCI Express Interface Spread Spectrum Requirements                     | 41  |

| Table 29:  | Standard Register Field Type Codes                                     | 55  |

| Table 30:  | Register Map Table for the Forward Bridge Mode Configuration Registers | 57  |

| Table 76:  | Register Map Table for the Reverse Bridge Mode Configuration Registers | 98  |

| Table 125: | Revision History                                                       | 142 |

## **List of Figures**

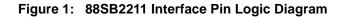

| Figure 1:  | 88SB2211 Interface Pin Logic Diagram               | 11 |

|------------|----------------------------------------------------|----|

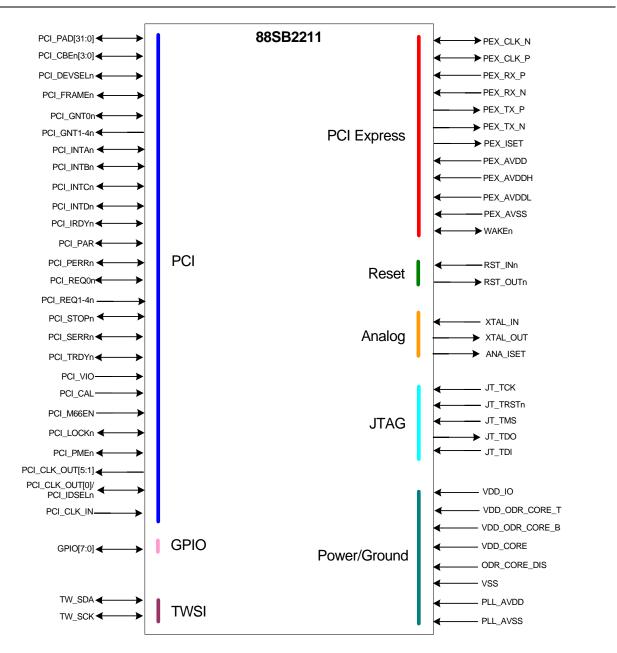

| Figure 2:  | 128 LQFP Pinout (Top View)                         | 21 |

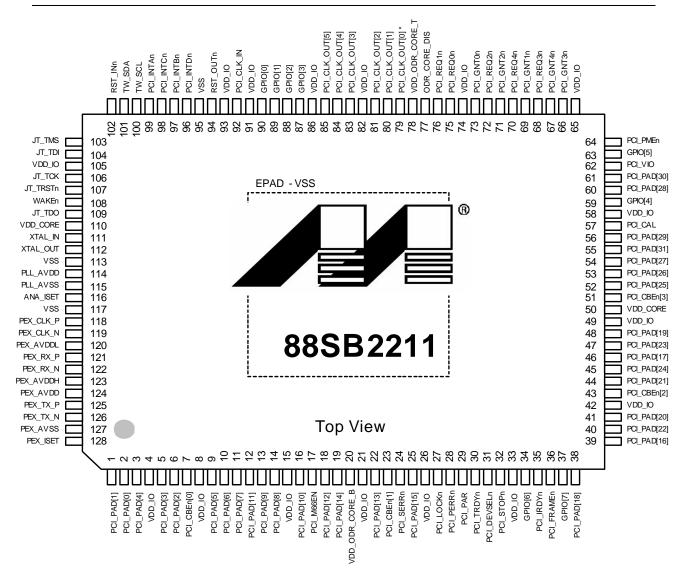

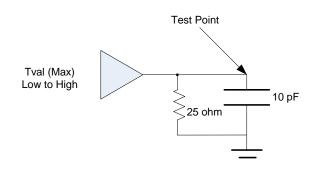

| Figure 3:  | Tval (Max) Rising Edge Test Load                   | 34 |

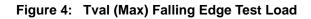

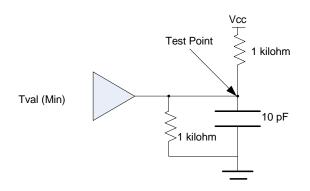

| Figure 4:  | Tval (Max) Falling Edge Test Load                  | 34 |

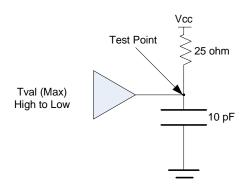

| Figure 5:  | Tval (Min) Test Load & Output Slew Rate Test Load  | 34 |

| Figure 6:  | PCI Interface Clock Waveform                       | 35 |

| Figure 7:  | PCI Interface Output Timing Measurement Conditions | 35 |

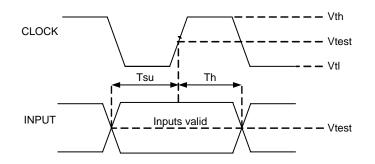

| Figure 8:  | PCI Interface Input Timing Measurement Conditions  | 36 |

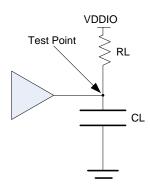

| Figure 9:  | TWSI Test Circuit                                  | 37 |

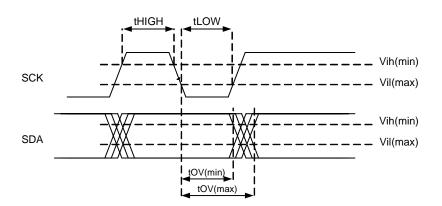

| Figure 10: | TWSI Output Delay AC Timing Diagram                | 38 |

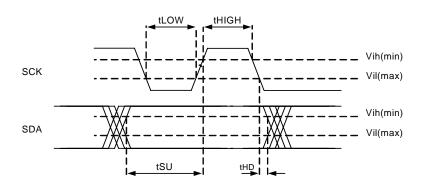

| Figure 11: | TWSI Input AC Timing Diagram                       | 38 |

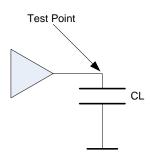

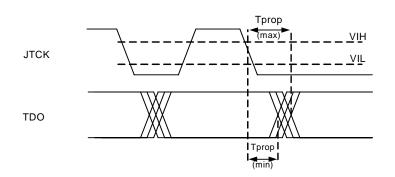

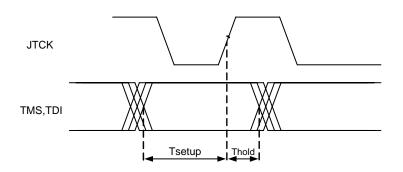

| Figure 12: | JTAG Interface Test Circuit                        | 39 |

| Figure 13: | JTAG Interface Output Delay AC Timing Diagram      |    |

| Figure 14: | JTAG Interface Input AC Timing Diagram             | 40 |

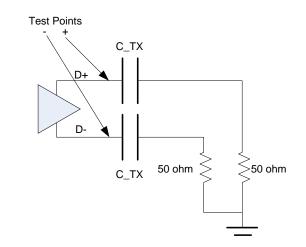

| Figure 15: | PCI Express Interface Test Circuit                 | 43 |

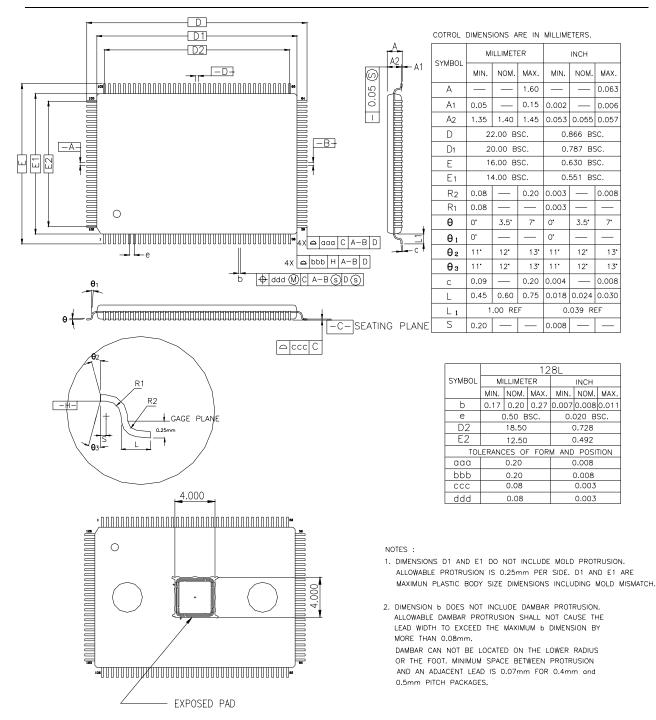

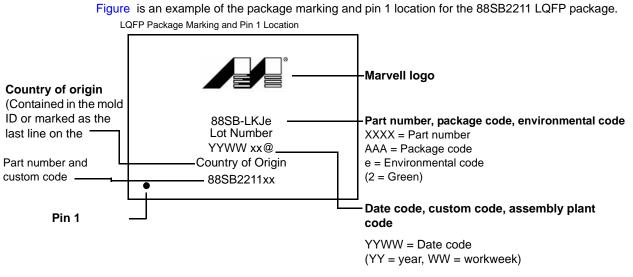

| Figure 16: | 128-Pin LQFP Package Diagram                       | 46 |

| Figure 17: | Sample Part Number                                 | 47 |

|            |                                                    |    |

## Preface

## **About This Document**

This datasheet provides the hardware specifications for the 88SB2211 PCI Express-to-PCI Bridge, including detailed pin information, configuration settings, electrical characteristics, and physical specifications. It also provides detailed definitions of the registers implemented in the device.

In this document the 88SB2211 is often referred to as the "device".

## **Related Documents**

- 88SB2211 Hardware Design Guidelines, Document number MV-S300975-00<sup>1</sup>.

- PCI Local Bus Specification, Revision 2.3

- PCI Express Base Specification, Revision 1.0a

- PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0

<sup>1.</sup> Contact your local Marvell<sup>®</sup> sales representative for information about receiving this document.

## **Document Conventions**

| The following conventions are followed in this document: |

|----------------------------------------------------------|

|----------------------------------------------------------|

| Signal Range                   | A signal name followed by a range enclosed in brackets represents a range of logically related signals. The first number in the range indicates the most significant bit (MSb) and the last number indicates the least significant bit (LSb).<br>Example: DB_Addr[12:0] |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active Low Signals #           | An n letter at the end of a signal name indicates that the signal's active state occurs when voltage is low.                                                                                                                                                            |

|                                | Example: INTn                                                                                                                                                                                                                                                           |

| State Names                    | State names are indicated in <i>italic</i> font.                                                                                                                                                                                                                        |

|                                | Example: linkfail                                                                                                                                                                                                                                                       |

| Register Naming<br>Conventions | Register field names are indicated by angle brackets.<br>Example: <reginit></reginit>                                                                                                                                                                                   |

|                                | Register field bits are enclosed in brackets.<br>Example: Field [1:0]                                                                                                                                                                                                   |

|                                | Register addresses are represented in hexadecimal format.<br>Example: 0x0                                                                                                                                                                                               |

|                                | Reserved: The contents of the register are reserved for internal use only or for future use.                                                                                                                                                                            |

|                                | A lowercase <n> in angle brackets in a register indicates that there are multiple registers with this name.</n>                                                                                                                                                         |

|                                | Example: Multicast Configuration Register <n></n>                                                                                                                                                                                                                       |

| Reset Values                   | Reset values have the following meanings:<br>0 = Bit clear<br>1 = Bit set                                                                                                                                                                                               |

| Abbreviations                  | Gb: gigabit<br>GB: gigabyte<br>Kb: kilobit<br>KB: kilobyte<br>Mb: megabit<br>MB: megabyte                                                                                                                                                                               |

| Numbering Conventions          | Unless otherwise indicated, all numbers in this document are decimal (base 10).<br>An 0x prefix indicates a hexadecimal number.<br>An 0b prefix indicates a binary number.                                                                                              |

# 1 Overview

The Marvell<sup>®</sup> 88SB2211 is a PCI Express-to-PCI bridge that connects legacy PCI parallel bus devices to the new advanced serial PCI Express interface. The 88SB2211 can also operate as a reverse bridge (PCI-to-PCI Express), enabling connection of PCI Express devices to the legacy PCI bus.

The 88SB2211 device is fully compliant with the *PCI Express to PCI/PCI-X Bridge Specification*, Revision 1.0, and supports a transparent forward or reverse bridging scheme. It is a single function bridge with a single PCI Express virtual channel (VC-0). It also supports the standard PCI-to-PCI bridge programming model.

The PCI Express port is fully compliant with the *PCI Express Base Specification*, Revision 1.0a. It supports an X1 link operation, allowing simultaneous 250 MBps throughput in the upstream and downstream directions. The PCI Express port contains an integrated PCI Express PHY, based on proven Marvell SERDES technology. For both downstream and upstream traffic, the 88SB2211 supports up to four outstanding non-posted requests. It supports a Maximum Payload Size (MPS) of 128 bytes, Advanced Error Reporting (AER) capability, lane polarity inversion for easy board routing, and advanced PCI Express Power Management (PM) features.

The PCI port is 32 bits wide and operates at 33 MHz. It is fully compliant with *PCI Local Bus Specification*, Revision 2.3. The 88SB2211 provides an internal arbiter and buffered clock outputs for up to five subordinate PCI devices. It supports 64-bit addressing, VGA and ISA addressing for legacy operation, and a tunable prefetch algorithm, which is useful for system throughput optimization.

Power management (PM) features include all conventional PCI D-states (software controlled), and PCI Express active state link PM mechanisms (hardware controlled). PME and Wake protocols are also supported, enabling the host system to further reduce power consumption.

The 88SB2211 also contains a single TWSI port for optional initialization, a single IEEE Standard 1149.1 JTAG port for testability, and eight General Purpose I/O pins (GPIOs) for further system customization.

The 88SB2211 can operate from a single 3.3V power rail, to reduce system cost. This is achieved by various On Die Regulators (ODRs) embedded in the device. To further optimize the power consumption, the ODRs can be bypassed.

# **2** Pin Information

The 88SB2211 is available in a 128-pin, LQFP package. Figure 1 is the pin logic diagram for the device.

## 2.1 Summary List of Functional Pins

Table 1 indicates the conventions used to identify I/O or O type pins and their pad type.

Table 1: Pin Assignment Table Conventions

| Abbreviation | Description                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | Input                                                                                                                                                  |

| 0            | Output                                                                                                                                                 |

| I/O          | Input/Output                                                                                                                                           |

| t/s          | Tri-State pin                                                                                                                                          |

| s/t/s        | Sustained Tri-State pin<br>The pin is driven to its inactive value for one cycle before float.<br>A pull-up is required to sustain the inactive value. |

| o/d          | Open Drain pin<br>The pin allows multiple drivers simultaneously (wire-OR connection).<br>A pull-up is required to sustain the inactive value.         |

| CML          | Current Mode Logic                                                                                                                                     |

| Analog       | Analog Supply/Signal                                                                                                                                   |

| Power        | VDD Power Supply                                                                                                                                       |

| GND          | Ground Supply                                                                                                                                          |

| PCI          | <ul> <li>PCI pad 3.3V according to the PCI standard</li> <li>5V tolerant</li> </ul>                                                                    |

| HCSL         | High-speed Current Steering Logic                                                                                                                      |

| Calib        | I/O Calibration Pin                                                                                                                                    |

Table 2 lists the pin count for each interface in the LQFP package.

Table 2: Functional Pin List Summary

| Interface   | Prefix | Count LQFP Package |

|-------------|--------|--------------------|

| PCI Express | PEX_   | 12                 |

| PCI         | PCI_   | 70                 |

| Reset       | RST_   | 2                  |

| TWSI        | TW_    | 2                  |

| JTAG        | JT_    | 5                  |

| GPIO        | GPIO   | 8                  |

| VDD_IO      | -      | 16                 |

| VDD_CORE    | -      | 2                  |

| Interface          | Prefix | Count LQFP Package |

|--------------------|--------|--------------------|

| VDD_ODR_CORE_T     | -      | 1                  |

| VDD_ODR_CORE_B     | -      | 1                  |

| ODR_CORE_DIS       | -      | 1                  |

| PLL_AVDD           | -      | 1                  |

| PLL_AVSS           | -      | 1                  |

| Analog             | -      | 3                  |

| Ground (VSS)       | -      | 3                  |

| NC (Not Connected) | -      | 0                  |

| Total              |        | 128                |

### Table 2: Functional Pin List Summary (Continued)

## 2.2 PCI Express Interface Pin Assignments

| Table 3: | PCI Express Interface Pin Assignments |

|----------|---------------------------------------|

|----------|---------------------------------------|

| Pin Name               | I/O / Pi   | n Type | Description                                                                                                                                                                                                                                            |

|------------------------|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PEX_CLK_P<br>PEX_CLK_N | I/O        | HSCL   | PCI Express Reference Clock<br>Differential pair of PCI Express 100 MHz reference clock.<br>The PCI Express clock direction is determined according to the reset<br>strapping (see Clock Mode Select in Table 12, Reset Configuration, on<br>page 23). |

| PEX_RX_P<br>PEX_RX_N   | I          | CML    | PCI Express Receive Lane<br>Differential pair of PCI Express receive data.                                                                                                                                                                             |

| PEX_TX_P<br>PEX_TX_N   | 0          | CML    | PCI Express Transmit Lane<br>Differential pair of PCI Express transmit data.                                                                                                                                                                           |

| PEX_ISET               | 0          | Analog | PCI Express Current Reference Connect to an external 6.04+/-1% k $\Omega$ resistor.                                                                                                                                                                    |

| PEX_AVDD               | 1          | Power  | Connect this pin to a decoupling capacitor.<br><b>NOTE:</b> When ODR is bypassed (see GPIO[3] in Table 12, Reset<br>Configuration, on page 23), this pin is the PCI Express PHY 2.5V<br>analog power supply.                                           |

| PEX_AVDDH              | I          | Power  | PCI Express PHY Filtered Power Supply (3.3V)                                                                                                                                                                                                           |

| PEX_AVDDL              | 1          | Power  | Connect this pin to a decoupling capacitor.<br><b>NOTE:</b> When ODR is bypassed (see GPIO[2] in Table 12, Reset<br>Configuration, on page 23), this pin is the PCI Express PHY 1.5V<br>analog power supply.                                           |

| PEX_AVSS               | 1          | Ground | PCI Express PHY Ground                                                                                                                                                                                                                                 |

| WAKEn                  | o/d<br>I/O | PCI    | PCI Express Wake (WAKE#)<br>When working in Forward Bridge mode, this signal is an output.<br>When working in Reverse Bridge mode, this signal is an input.                                                                                            |

## 2.3 PCI 32-bit Interface Pin Assignments

| Table 4: PCI 32-bit Bus Interface Pin Assignment | Table 4: | oit Bus Interface Pin Assignments |

|--------------------------------------------------|----------|-----------------------------------|

|--------------------------------------------------|----------|-----------------------------------|

| Pin Name      | I/O / Pin Type |     | Description                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------|----------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PCI_VIO       | I              | PCI | PCI Voltage I/O<br>Clamping reference voltage for PCI (3.3V or 5V).                                                                                                                                                                                                                                           |  |  |  |

| PCI_M66EN     | 1              | PCI | PCI 66 MHz Enable<br>The 88SB2211 does not support 66 MHz PCI. Therefore, pull this pin down<br>to 0.                                                                                                                                                                                                         |  |  |  |

| PCI_PAD[31:0] | t/s I/O        | PCI | PCI Address/Data<br>32-bit PCI multiplexed address/data bus.<br>Driven by the transaction master during the address phase and the write<br>data phase.<br>Driven by the target device during the read data phase.                                                                                             |  |  |  |

| PCI_CBEn[3:0] | t/s I/O        | PCI | PCI Command/Byte Enable<br>A multiplexed command/byte-enable bus, driven by the transaction master.<br>Contains the command during the address phase, and the byte-enable<br>during data phase.                                                                                                               |  |  |  |

| PCI_PAR       | t/s I/O        | PCI | PCI Parity<br>Even parity is calculated for PCI_PAD[31:0] and PCI_CBEn[3:0].<br>Driven by the transaction master for the address phase and the write data<br>phase.<br>This pin is driven by the target for the read data phase.                                                                              |  |  |  |

| PCI_FRAMEn    | s/t/s<br>I/O   | PCI | PCI Frame<br>Asserted by the transaction master to indicate the beginning of a<br>transaction.<br>The master de-asserts PCI_FRAMEn to indicate that the next data phase is<br>the final data phase transaction.                                                                                               |  |  |  |

| PCI_DEVSELn   | s/t/s<br>I/O   | PCI | PCI Device Select<br>Asserted by the target of the current access.<br>As a master, the target device is expected to assert PCI_DEVSELn within<br>five bus cycles. Otherwise, it aborts the cycle.<br>As a target, PCI_DEVSELn is asserted at a medium speed; two cycles after<br>the assertion of PCI_FRAMEn. |  |  |  |

| PCI_IRDYn     | s/t/s<br>I/O   | PCI | PCI Initiator Ready<br>Asserted by the transaction master to indicate it is ready to complete the<br>current data phase of the transaction. A data phase is completed when<br>both PCI_TRDYn and PCI_IRDYn are asserted.                                                                                      |  |  |  |

| PCI_TRDYn     | s/t/s<br>I/O   | PCI | PCI Target Ready<br>Asserted by the target to indicate it is ready to complete the current data<br>phase of the transaction. A data phase is completed when both<br>PCI_TRDYn and PCI_IRDYn are asserted.                                                                                                     |  |  |  |

| PCI_STOPn     | s/t/s<br>I/O   | PCI | PCI Stop<br>Asserted by target to indicate transaction termination.<br>Used by a target device to generate a Retry, Disconnect, or Target Abort<br>termination signal.                                                                                                                                        |  |  |  |

| Pin Name I/O / Pin Type                                       |                                             |       | Description                                                                                                                                                                                                                  |  |  |

|---------------------------------------------------------------|---------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PCI_REQ0n<br>PCI_REQ1n<br>PCI_REQ2n<br>PCI_REQ3n<br>PCI_REQ4n | /O<br> <br> <br> <br>                       | PCI   | PCI Bus Request<br>When the internal PCI Arbiter is used, these pins are used as the request<br>inputs from the external agents.<br>When an external arbiter is used, PCI_REQ0n is used as the REQn output<br>of the bridge. |  |  |

| PCI_GNT0n<br>PCI_GNT1n<br>PCI_GNT2n<br>PCI_GNT3n<br>PCI_GNT4n | t/s I/O<br>t/s O<br>t/s O<br>t/s O<br>t/s O | PCI   | PCI Bus Grant<br>When the internal PCI Arbiter is used, these pins are used as the grant<br>outputs for the external agents.<br>When an external arbiter is used, PCI_GNT0n is used as the GNTn input of<br>the bridge.      |  |  |

| PCI_PERRn                                                     | s/t/s<br>I/O                                | PCI   | PCI Parity Error<br>Asserted when a data parity error is detected.<br>Asserted by a target device in response to bad address or write data parity,<br>or by the master device in response to bad read data parity.           |  |  |

| PCI_SERRn                                                     | o/d<br>I/O                                  | PCI   | PCI System Error<br>Asserted when a system error is detected.                                                                                                                                                                |  |  |

| PCI_LOCKn                                                     | I/O                                         | PCI   | PCI Lock                                                                                                                                                                                                                     |  |  |

| PCI_PMEn                                                      | o/d<br>I/O                                  | PCI   | PCI Power Management Event                                                                                                                                                                                                   |  |  |

| PCI_CLK_OUT[0]<br>PCI_IDSELn                                  | O<br>I                                      | PCI   | PCI Clock Output/PCI IDSEL<br><b>NOTE:</b> In Reverse Bridge mode, PCI_CLK_OUT[0] acts as the<br>device PCI_IDSELn pin (input).                                                                                              |  |  |

| PCI_CLK_OUT[5:1]                                              | 0                                           | PCI   | PCI Clock Output                                                                                                                                                                                                             |  |  |

| PCI_CLK_IN                                                    | I                                           | PCI   | PCI Clock Input                                                                                                                                                                                                              |  |  |

| PCI_INTAn                                                     | o/d<br>I/O                                  | PCI   | PCI Interrupt Request A                                                                                                                                                                                                      |  |  |

| PCI_INTBn                                                     | o/d<br>I/O                                  | PCI   | PCI Interrupt Request B                                                                                                                                                                                                      |  |  |

| PCI_INTCn                                                     | o/d<br>I/O                                  | PCI   | PCI Interrupt Request C                                                                                                                                                                                                      |  |  |

| PCI_INTDn                                                     | o/d<br>I/O                                  | PCI   | PCI Interrupt Request D                                                                                                                                                                                                      |  |  |

| PCI_CAL                                                       | 1                                           | Calib | PCI Pads Calibration Input<br>(Refer to the 88SB2211 Hardware Design Guidelines for a description of<br>the pin connectivity).                                                                                               |  |  |

### Table 4: PCI 32-bit Bus Interface Pin Assignments (Continued)

## 2.4 Reset Pin Assignments

| Pin Name | I/O / Pi   | n Type | Description                                                                                                                                                                                                               |  |  |

|----------|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RST_INn  | _INn I PCI |        | <ul> <li>Reset In</li> <li>When working in Forward Bridge mode, this is the PCI Express reset input signal (PERST#).</li> <li>When working in Reverse Bridge mode, this is the PCI reset input signal (PRST#).</li> </ul> |  |  |

| RST_OUTn | 0          | PCI    | <ul> <li>Reset Out</li> <li>When working in Forward Bridge mode, this is the PCI reset output signal.</li> <li>When working in Reverse Bridge mode, this is the PCI Express reset output signal.</li> </ul>               |  |  |

### Table 5: Reset Pin Assignments

## 2.5 TWSI Interface Pin Assignments

| Table 6: | <b>TWSI Interface Pin Assignments</b> |

|----------|---------------------------------------|

|----------|---------------------------------------|

| Pin Name         I/O / Pin Type           TW_SDA         o/d I/O         PCI |         | n Type | Description                                                                                                                                                                                                                                                                                                                              |  |  |

|------------------------------------------------------------------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                              |         | PCI    | TWSI Port Serial Data<br>Address or write data driven by the TWSI master or read response data<br>driven by the TWSI slave.<br><b>NOTE:</b> The 88SB2211 slave address is 7'h2F (7'b0101111).<br>Since this pin contains and internal pull-up, it can be left<br>unconnected when not used.<br>If used, it requires an external pull-up. |  |  |

| TW_SCL                                                                       | o/d I/O | PCI    | TWSI Port Serial Clock<br>Serves as output when acting as a TWSI master.<br>Serves as input when acting as a TWSI slave.<br><b>NOTE:</b> Since this pin contains and internal pull-up, it can be left<br>unconnected when not used.<br>If used, it requires an external pull-up.                                                         |  |  |

## 2.6 JTAG Interface Pin Assignments

### Table 7: JTAG Pin Assignments

| Pin Name | I/O / Pi | n Type | Description                                                                                                                                                         |  |  |

|----------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| JT_TCK   | I        | PCI    | JTAG Clock<br>Clock input for the JTAG controller.<br><b>NOTE:</b> This pin is internally pulled down to 0.                                                         |  |  |

| JT_TRSTn | 1        | PCI    | JTAG Reset<br>When asserted, resets the JTAG controller.<br><b>NOTE:</b> This pin is internally pulled down to 0. <sup>1</sup>                                      |  |  |

| JT_TMS   | 1        | PCI    | Core JTAG Mode Select<br>Controls the Core JTAG controller state.<br>Sampled with the rising edge of JT_TCK.<br><b>NOTE:</b> This pin is internally pulled up to 1. |  |  |

| JT_TDO   | 0        | PCI    | JTAG Data Out<br>Driven on the falling edge of JT_TCK.                                                                                                              |  |  |

| JT_TDI   | I        | PCI    | JTAG Data In<br>JTAG serial data input. Sampled with the JT_TCK rising edge.<br><b>NOTE:</b> This pin is internally pulled up to 1.                                 |  |  |

1. If this pull-down conflicts with other devices, the JTAG tool must not use this signal. This signal is not mandatory for the JTAG interface, since the TAP can be reset by driving the JT\_TMS signal HIGH for five JT\_TCK cycles.

## 2.7 GPIO Interface Pin Assignments

| Pin Name  | I/O / Pin Type |     | Description                              |

|-----------|----------------|-----|------------------------------------------|

| GPIO[7:0] | t/s I/O        | PCI | General Purpose Pin<br>Various functions |

## 2.8 Analog Interface Pin Assignments

Table 9: Analog Interface Pin Assignments

| Pin Name | I/O / Pin Type |  | Description                                                                                                                                                                            |  |  |

|----------|----------------|--|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| XTAL_IN  | I Analog       |  | Crystal Input/Reference Clock Input 25 MHz.<br>When using a crystal, this pin is used as the XTAL_IN input.<br><b>NOTE:</b> When not using crystal, this pin must be pulled down to 0. |  |  |

| XTAL_OUT | O Analog       |  | Crystal Output<br><b>NOTE:</b> Leave unconnected if a crystal is not used.                                                                                                             |  |  |

| ANA_ISET | O Analog       |  | O Analog Current Reference<br>Connect to an external 6.04 kΩ resistor.                                                                                                                 |  |  |

## 2.9 Power/Ground Pin Assignments

| Pin Name           | I/O / Pin Type |        | Description                                                                                                                                                     |  |

|--------------------|----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VDD_IO             | I/O Power      |        | 3.3V power supply for all interfaces, excluding PCI Express interface.                                                                                          |  |

| VDD_ODR_<br>CORE_T | I              | Power  | 3.3V filtered power supply for the core voltage (1.2V) ODR.                                                                                                     |  |

| VDD_ODR_<br>CORE_B | I              | Power  | 3.3V filtered power supply for the core voltage (1.2V) ODR.                                                                                                     |  |

| VDD_CORE           | 1              | Power  | Connect these pins to decoupling capacitors (0.1 μF).<br><b>NOTE:</b> When ODR is bypassed (ODR_CORE_DIS = 1), these pins are th<br>VDD_CORE 1.2V power supply. |  |

| ODR_CORE_DIS       | 1              | Analog | Core Voltage On-Die-Regulator Control <ul> <li>VSS—Core On-Die-Regulator Enabled (default)</li> <li>3.3V—Core On-Die-Regulator Disabled (Bypassed)</li> </ul>   |  |

| VSS                | I              | GND    | Ground                                                                                                                                                          |  |

| PLL_AVDD           | I              | Power  | PLL 3.3V Filtered Power                                                                                                                                         |  |

| PLL_AVSS           | I              | GND    | PLL Ground                                                                                                                                                      |  |

### Table 10: Power/Ground Interface Pin Assignments

# **3** 88SB2211 Pinout

This section provides the pin map and pinout table for the 88SB2211—128 LQFP. See 2 "Pin Information" on page 11 for a detailed description of the pin signals.

\* In Reverse Bridge mode, pin 79 acts as the device PCI\_IDSELn pin (input).

| Pin # | Pin Name       | Pin # | Pin Nam e        | Pin # | Pin Nam e  |

|-------|----------------|-------|------------------|-------|------------|

| 1     | PCI_PAD[1]     | 44    | PCI_PAD[21]      | 87    | GPIO[3]    |

| 2     | PCI_PAD[0]     | 45    | PCI_PAD[24]      | 88    | GPIO[2]    |

| 3     | PCI_PAD[4]     | 46    | PCI_PAD[17]      | 89    | GPIO[1]    |

| 4     | VDD_IO         | 47    | PCI_PAD[23]      | 90    | GPIO[0]    |

| 5     | PCI_PAD[3]     | 48    | PCI_PAD[19]      | 91    | VDD_IO     |

| 6     | PCI_PAD[2]     | 49    | VDD_IO           | 92    | PCI_CLK_IN |

| 7     | PCI_CBEn[0]    | 50    | VDD_CORE         | 93    | VDD_IO     |

| 8     | VDD_IO         | 51    | PCI_CBEn[3]      | 94    | RST_OUTn   |

| 9     | PCI_PAD[5]     | 52    | PCI_PAD[25]      | 95    | VSS        |

| 10    | PCI_PAD[6]     | 53    | PCI_PAD[26]      | 96    | PCI_INTDn  |

| 11    | PCI_PAD[7]     | 54    | PCI_PAD[27]      | 97    | PCI_INTBn  |

| 12    | PCI_PAD[11]    | 55    | PCI_PAD[31]      | 98    | PCI_INTCn  |

| 13    | PCI_PAD[9]     | 56    | PCI_PAD[29]      | 99    | PCI_INTAn  |

| 14    | PCI_PAD[8]     | 57    | PCI_CAL          | 100   | TW_SCL     |

| 15    | VDD_IO         | 58    | VDD_IO           | 101   | TW_SDA     |

| 16    | PCI_PAD[10]    | 59    | GPIO[4]          | 102   | RST_INn    |

| 17    | PCI_M66EN      | 60    | PCI_PAD[28]      | 103   | JT_TMS     |

| 18    | PCI_PAD[12]    | 61    | PCI_PAD[30]      | 104   | JT_TDI     |

| 19    | PCI_PAD[14]    | 62    | PCI_VIO          | 105   | VDD_IO     |

| 20    | VDD_ODR_CORE_B | 63    | GPIO[5]          | 106   | JT_TCK     |

| 21    | VDD_IO         | 64    | PCI_PMEn         | 107   | JT_TRSTn   |

| 22    | PCI_PAD[13]    | 65    | VDD_IO           | 108   | WAKEn      |

| 23    | PCI_CBEn[1]    | 66    | PCI_GNT3n        | 109   | JT_TDO     |

| 24    | PCI_SERRn      | 67    | PCI_GNT4n        | 110   | VDD_CORE   |

| 25    | PCI_PAD[15]    | 68    | PCI_REQ3n        | 111   | XTAL_IN    |

| 26    | VDD_IO         | 69    | PCI_GNT1n        | 112   | XTAL_OUT   |

| 27    | PCI_LOCKn      | 70    | PCI_REQ4n        | 113   | VSS        |

| 28    | PCI_PERRn      | 71    | PCI_GNT2n        | 114   | PLL_AVDD   |

| 29    | PCI_PAR        | 72    | PCI_REQ2n        | 115   | PLL_AVSS   |

| 30    | PCI_TRDYn      | 73    | PCI_GNT0n        | 116   | ANA_ISET   |

| 31    | PCI_DEVSELn    | 74    | VDD_IO           | 117   | VSS        |

| 32    | PCI_STOPn      | 75    | PCI_REQ0n        | 118   | PEX_CLK_P  |

| 33    | VDD_IO         | 76    | PCI_REQ1n        | 119   | PEX_CLK_N  |

| 34    | GPIO[6]        | 77    | ODR_CORE_DIS     | 120   | PEX_AVDDL  |

| 35    | PCI_IRDYn      | 78    | VDD_ODR_CORE_T   | 121   | PEX_RX_P   |

| 36    | PCI_FRAMEn     | 79    | PCI_CLK_OUT[0] * | 122   | PEX_RX_N   |

| 37    | GPIO[7]        | 80    | PCI_CLK_OUT[1]   | 123   | PEX_AVDDH  |

| 38    | PCI_PAD[18]    | 81    | PCI_CLK_OUT[2]   | 124   | PEX_AVDD   |

| 39    | PCI_PAD[16]    | 82    | VDD_IO           | 125   | PEX_TX_P   |

| 40    | PCI_PAD[22]    | 83    | PCI_CLK_OUT[3]   | 126   | PEX_TX_N   |

| 41    | PCI_PAD[20]    | 84    | PCI_CLK_OUT[4]   | 127   | PEX_AVSS   |

| 42    | VDD_IO         | 85    | PCI_CLK_OUT[5]   | 128   | PEX_ISET   |

| 43    | PCI_CBEn[2]    | 86    | VDD_IO           |       |            |

### Table 11: 128 LQFP Pinout Pin List by Pin Number

\* In Reverse Bridge mode, pin 79 acts as the device PCI\_IDSELn pin (input).

# **4** Reset Configuration

## 4.1 Pins Sample Configuration

Unless specifically noted, all reset sampled pins are sampled upon de-assertion of RST\_INn. Table 12 describes the reset pins configuration.

Table 12: Reset Configuration

| Pin         | Configuration Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI_M66EN   | PCI 66 MHz Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 0 = Disabled<br>1 = Enabled<br>Sampled upon de-assertion of PCI_PRSTn.<br><b>NOTE:</b> Since the 88SB2211 does not support PCI 66 MHz, this pin must be pulled down to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PCI_REQn[0] | PCI Slot 0 Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | Enables both PCI_CLK_OUT[0] output and PCI_REQn[0] input. When disabled, the clock output is<br>forced to zero, and the request input is internally masked.<br>0 = Disabled<br>1 = Enabled<br><b>NOTE:</b> Internally pulled up to 1.<br>When working with an external arbiter, PCI_CLK_OUT[0] is enabled by default, since this<br>signal functions as PCI_REQ output and the PCI specification requires a pull up on this<br>signal. Shutting down PCI_CLK_OUT[0] is only supported via the Table 52, Forward Bridge<br>PCI Clock Output Control Register, on page 81 or Table 101, Reverse Bridge PCI Clock<br>Output Control Register, on page 124 access. |

| PCI_REQn[1] | PCI Slot 1 Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | Enables both PCI_CLK_OUT[1] output and PCI_REQn[1] input. When disabled, the clock output is forced to zero, and the request input is internally masked.<br>0 = Disabled<br>1 = Enabled<br><b>NOTE:</b> Internally pulled up to 1.                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | When working with the internal arbiter providing REQ/GNT coupled to slot 1, this signal must<br>be pulled up, according to the PCI specification. in this case, shutting down<br>PCI_CLK_OUT[1] is only supported via the Table 52, Forward Bridge PCI Clock Output<br>Control Register, on page 81 or Table 101, Reverse Bridge PCI Clock Output Control<br>Register, on page 124 access.                                                                                                                                                                                                                                                                     |

| Table 12: | Reset | Configuration | (Continued) |

|-----------|-------|---------------|-------------|

|-----------|-------|---------------|-------------|

| Pin         | Configuration Function                                                                                                                                                                                                                                                                                                                                                     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI_REQn[2] | PCI Slot 2 Enable                                                                                                                                                                                                                                                                                                                                                          |

|             | Enables both PCI_CLK_OUT[2] output and PCI_REQn[2] input. When disabled, the clock output is forced to zero, and the request input is masked internally.<br>0 = Disabled<br>1 = Enabled<br><b>NOTE:</b> Internally pulled up to 1.                                                                                                                                         |

|             | When working with the internal arbiter providing REQ/GNT coupled to slot 2, this signal must be pulled up according to the PCI specification. Shutting down PCI_CLK_OUT[2] in this case is only supported via Table 52, Forward Bridge PCI Clock Output Control Register, on page 81 or Table 101, Reverse Bridge PCI Clock Output Control Register, on page 124 access.   |

| PCI_REQn[3] | PCI Slot 3 Enable                                                                                                                                                                                                                                                                                                                                                          |

|             | Enables both PCI_CLK_OUT[3] output and PCI_REQn[3] input. When disabled, the clock output is forced to zero, and the request input is internally masked.<br>0 = Disabled<br>1 = Enabled<br><b>NOTE:</b> Internally pulled up to 1.                                                                                                                                         |

|             | When working with the internal arbiter providing REQ/GNT coupled to slot 3, this signal must be pulled up according to the PCI specification. In this case, shutting down PCI_CLK_OUT[3] is only supported via Table 52, Forward Bridge PCI Clock Output Control Register, on page 81 or Table 101, Reverse Bridge PCI Clock Output Control Register, on page 124 access.  |

| PCI_REQn[4] | PCI Slot 4 Enable                                                                                                                                                                                                                                                                                                                                                          |

|             | Enables both PCI_CLK_OUT[4] output and PCI_REQn[4] input. When disabled, the clock output is forced to 0, and the request input is masked internally.<br>0 = Disabled<br>1 = Enabled<br><b>NOTE:</b> Internally pulled up to 1.                                                                                                                                            |

|             | When working with the internal arbiter providing REQ/GNT coupled to slot 4, this signal must be pulled up, according to the PCI specification. In this case, shutting down PCI_CLK_OUT[4] is only supported via Table 52, Forward Bridge PCI Clock Output Control Register, on page 81 or Table 101, Reverse Bridge PCI Clock Output Control Register, on page 124 access. |

| GPIO[0]     | Serial ROM Initialization                                                                                                                                                                                                                                                                                                                                                  |

|             | 0 = Disabled<br>1 = Enabled<br><b>NOTE:</b> Internally pulled down to 0.                                                                                                                                                                                                                                                                                                   |

| Pin           | Configuration Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO[1]       | PCI Express Reference Clock Source Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 0 = 100 MHz differential reference clock<br>1 = 125 MHz single-ended reference clock<br><b>NOTE:</b> Internally pulled down to 0.<br>Refer to Clock Mode Select reset configuration for additional information on the reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               | clock options.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GPIO[2]       | 1.5V On Die Regulator Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               | 0 = 1.5V ODR Enabled.<br>1 = 1.5V ODR Disabled. 1.5V fed directly from the board.<br><b>NOTE:</b> Internally pulled down to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GPIO[3]       | 2.5V On Die Regulator Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               | 0 = 2.5V ODR Enabled.<br>1 = 2.5V ODR Disabled. 2.5V fed directly from the board.<br><b>NOTE:</b> Internally pulled down to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PCI_GNTn[1]   | Internal PCI Arbiter Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|               | 0 = Disabled<br>1 = Enabled<br><b>NOTE:</b> Internally pulled up to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PCI_GNTn[3:2] | Clock Mode Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|               | <ul> <li>0 = XTAL Clock Source mode<br/>Reference clock to the PLL is XTAL_IN (25 MHz).<br/>PEX_CLK_N and PEX_CLK_P are inputs.</li> <li>1 = XTAL Clock Source mode (PCI Express Clock Internal Generation)<br/>Reference clock to the PLL is XTAL_IN (25 MHz).<br/>PEX_CLK_N and PEX_CLK_P are outputs.<br/>NOTE: When working in this mode, only PCI agents 0, 1, and 2 are supported in the device<br/>internal arbiter.</li> <li>2 = PCI Clock Source mode<br/>Reference clock to the PLL is PCI_CLK_IN (applicable only when the PCI clock period is exactly<br/>30 ns).<br/>PEX_CLK_N and PEX_CLK_P are outputs.</li> <li>3 = PCI Express Clock Source mode<br/>Reference clock to the PLL are PEX_CLK_N and PEX_CLK_P. (inputs)<br/>See the 88SB2211 Hardware Design Guidelines for additional information about the clock modes.<br/>NOTE: PCI_GNTn[3] and PCI_GNTn[2] are internally pulled up to 1.</li> </ul> |

| PCI_GNTn[4]   | Bridge Mode Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               | 0 = Reverse Bridge mode—The host is on PCI side.<br>1 = Forward Bridge mode—The host is on PCI Express side.<br><b>NOTE:</b> Internally pulled up to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

PCI\_CLK\_OUT[5] is automatically disabled when all five PCI\_CLK\_OUT[4:0] pins are disabled.

# **Electrical Specifications (Preliminary)**

The numbers specified in this section are PRELIMINARY and SUBJECT TO CHANGE.

#### 5.1 **Absolute Maximum Ratings**

| Parameter            | Min  | Max | Units | Comments                                                             |

|----------------------|------|-----|-------|----------------------------------------------------------------------|

| VDD_CORE             | -0.5 | 1.5 | V     | Core voltage                                                         |

| VDD_ODR_CORE_B       | -0.5 | 4.0 | V     | Input voltage for: Core ODR                                          |

| VDD_ODR_CORE_T       | -0.5 | 4.0 | V     | Input voltage for: Core ODR                                          |

| ODR_CORE_DIS         | -0.5 | 4.0 | V     | Core ODR disable signal                                              |

| PLL_AVDD             | -0.5 | 4.0 | V     | Analog supply for the internal PLL                                   |

| VDD_IO <sup>1</sup>  | -0.5 | 4.0 | V     | I/O voltage for: PCI, TWSI and JTAG interfaces                       |

| PCI_VIO <sup>1</sup> | -0.5 | 6.0 | V     | I/O voltage for: PCI interface                                       |

| PEX_AVDDH            | -0.5 | 4.0 | V     | High voltage for: PCI Express interface                              |

| PEX_AVDD             | -0.5 | 3.0 | V     | Analog voltage for:<br>PCI Express interface when bypassing 2.5V ODR |

| PEX_AVDDL            | -0.5 | 1.8 | V     | Analog voltage for:<br>PCI Express interface when bypassing 1.5V ODR |